- IC 设计流程中,EDA 工具起到了必不可少的作用;

- 设计流程中,每一层到下一层都是一对多的关系;

- 在各个层次之间转换时,需要考虑优化、验证;

- AI for EDA:

- 传统方法:针对一个特殊任务设计一个网络,通过数据驱动的方式做一些预测;通过预测数据来强化学习;

- 但这种方法缺乏泛化能力:不同电路设计具有显著的结构和功能多样性(很难说是同分布的,而小网络对 OOD 场景效果不好);

- LLM 方法:大量数据训练,很少 OOD;

- 传统方法:针对一个特殊任务设计一个网络,通过数据驱动的方式做一些预测;通过预测数据来强化学习;

- LLM for EDA:

- 基础应用:生成 HDL 代码,或者做半导体知识问答;

- 但 HDL 正确性和 PPA 都无法保证;

- LLM 做 HDL 代码解释还可以;但生成测试用例效果不是很好;做 reasoning 效果更差(如何设计来实现指定的输入输出);

- 认为 LLM 不能解决 EDA 中复杂的优化和验证问题;

- Ilya 宣称压缩即智能;电路数据跟其他数据具有显著的差别:文本或图像数据中,已经包含了“你想压缩的数据”;然而电路描述的是一个计算过程的数据,而 LLM 无法有效的压缩相关的信息;

- 解决方法:需要一个专用的模型,来对电路这种特殊的数据,设计能够表征计算信息的 native 模型;(比较大胆的假设,“软件代码也是一样的,只是没人做”听起来不太站得住脚)

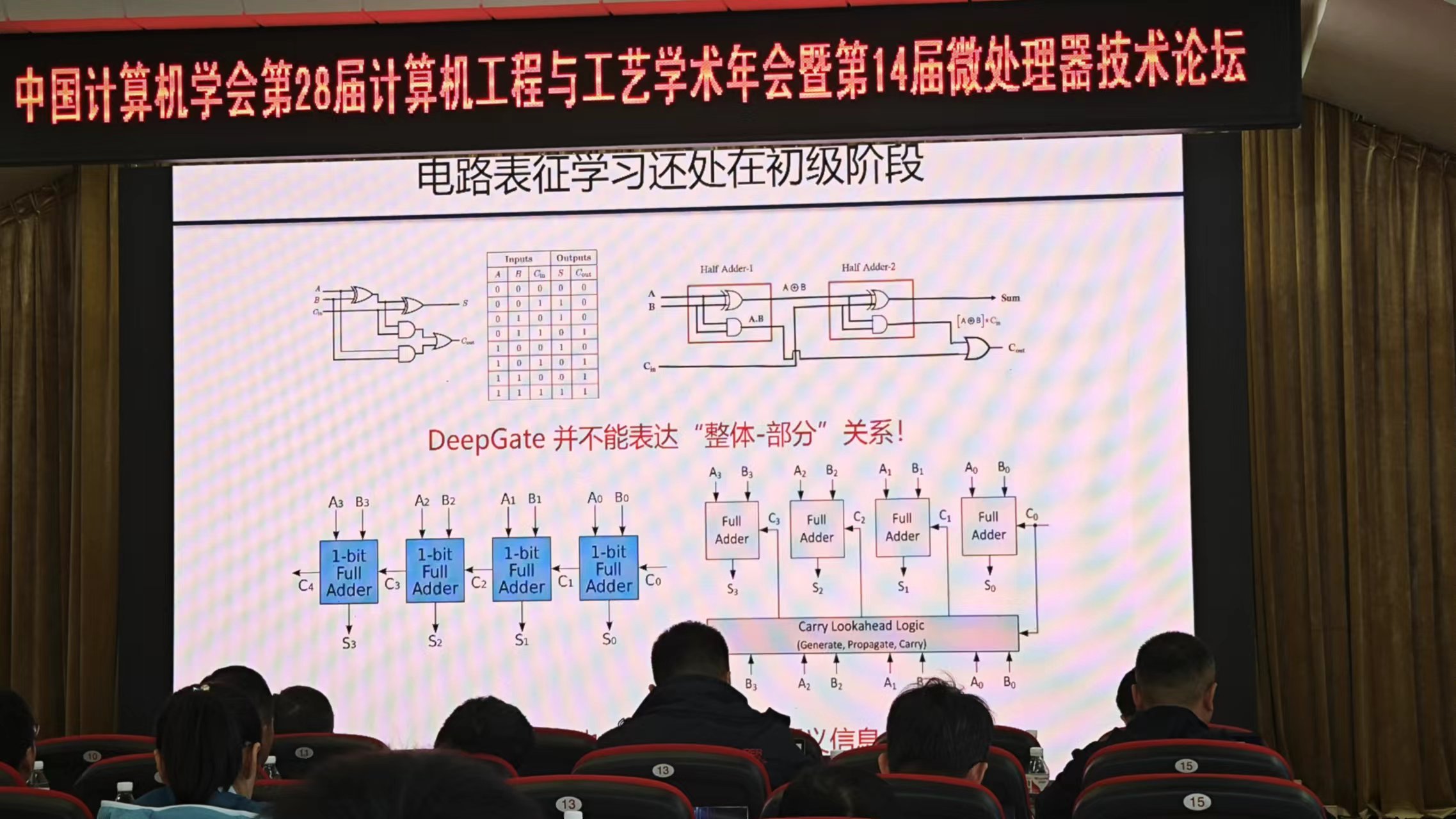

- DeepGate@DAC22 :预训练任务为预测节点逻辑概率;

- DeepGate2@ICCAD23 :引入更多预训练任务,将结构和功能分开进行表征学习;

- DeepGate3@ICCAD24 :将 DeepGate 2 作为 tokenizer,结合 transformer,支持门级和子图级表征;

- Ilya 宣称压缩即智能;电路数据跟其他数据具有显著的差别:文本或图像数据中,已经包含了“你想压缩的数据”;然而电路描述的是一个计算过程的数据,而 LLM 无法有效的压缩相关的信息;

- 电路的表征学习还在一个初级阶段:无法表达“整体-部分”之间的关系;

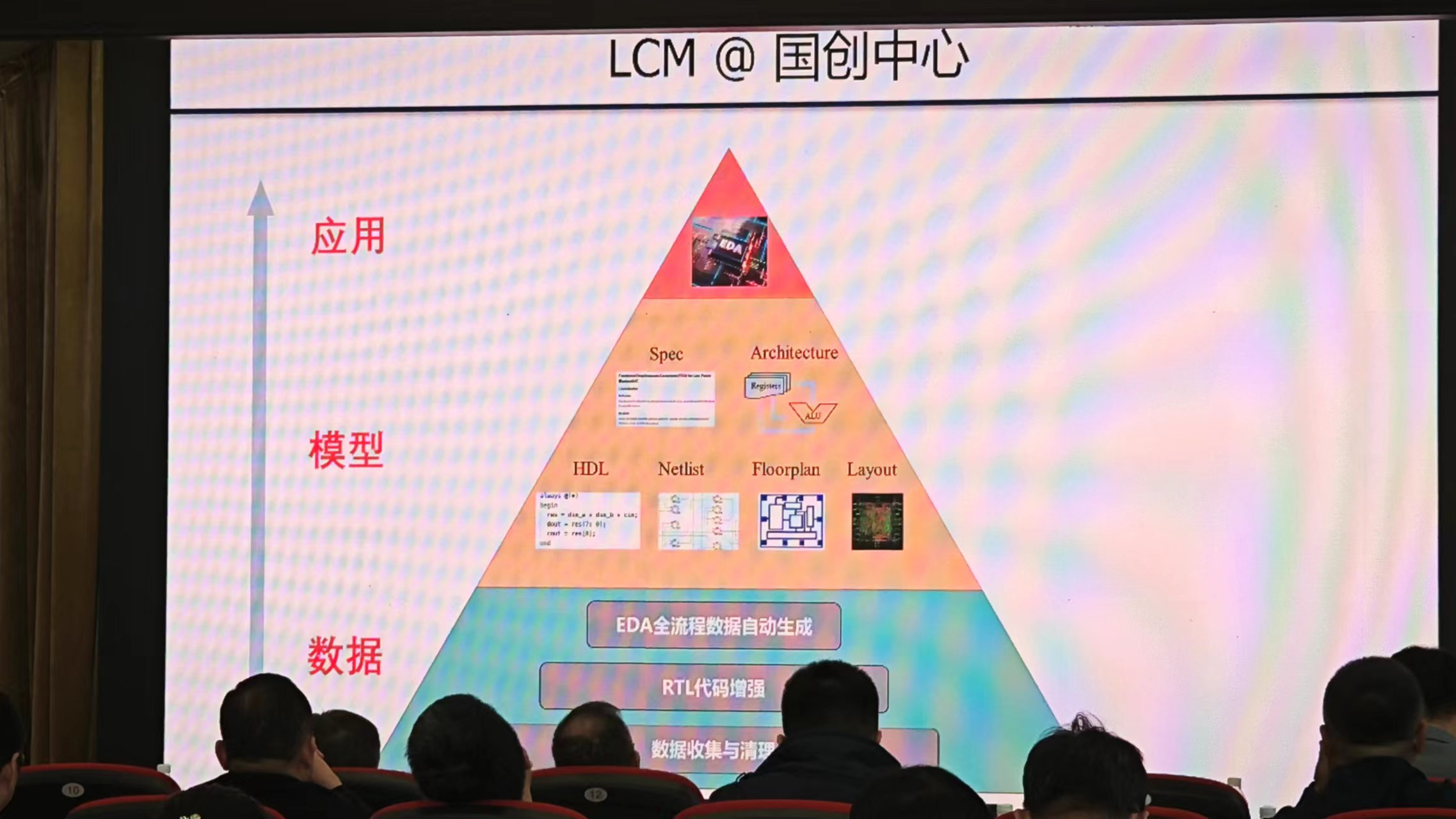

- 因此将芯片设计流程看成一个多模态转换过程:从 spec 描述,到功能建模,到 HDL 描述,到逻辑综合,到物理设计;

- 所以要做的是强约束下的多模态转换。各个模态描述的是同一功能,只是实现层次和细节有所不同;

- 引入大电路模型:

- 相当于在压缩跨阶段的相关信息,不再每一阶段分别学习表征,而是“分久必合”;

- 训练出来后,可以提升现有 EDA 工具的效率,也可以创建新的工具;

- 数据来源:OpenCores,RV,OpenROAD 等;开源电路数据相对于软件少很多,然而实际的电路种类是有限的,而且在实现上都可以分为数据通路和控制通路;

- 算力来源:GPU 服务器;

- 网络架构设计:基本上不太需要发明新的架构了,而是考虑该训练什么;

- LCM 的应用:

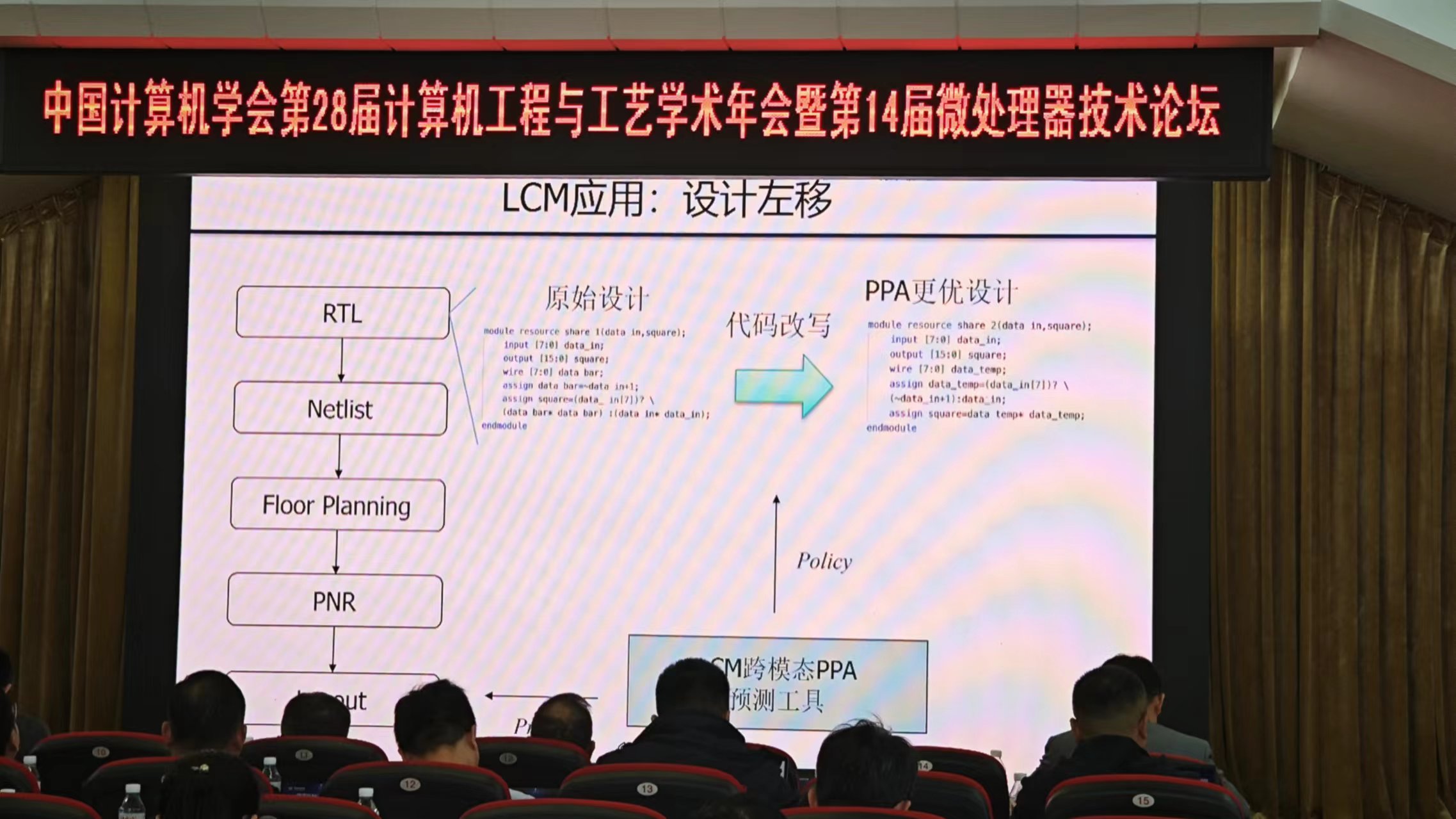

- 设计左移:在 RTL 阶段做优化;

- 验证:比如多位宽运算电路的电路验证,不一定要在网表阶段做验证,可以用 LCM 做反编译,在高层次进行验证;

- 电路生成:直接输入 spec 生成 GDSII;虽然不太可能,但不过也许可以看出哪个电路设计更好;

- 设计左移:在 RTL 阶段做优化;

- LCM 论文:Large Circult Model

- 阶段性成果:

- 分为三层:

- 数据层:已经收集超过 22 万个电路设计文件,超过一亿行设计代码;(说今年开源,能弄到吗?);RTL 代码是最重要的,同一份 RTL 代码可以生成大量下层数据;

- 模型层:

- DeepRTL:采用 Encoder-Decoder 架构,能够对百行的 Verilog 代码给出准确解释;

- DeepLayout:

- SAT:

- DeepDatapath:设计高性能累加树可建模为组合优化问题,设计空间巨大难以搜索;通过 diffusion based 方法进行优化指导;

- 应用层:

- 设计左移什么的;

- 分为三层:

- 基础应用:生成 HDL 代码,或者做半导体知识问答;